# Soc を用いた (種に選びまチョウ!) システム設計の勘所!!!

0000 0001

CQ出版社

## SoC を用いた システム設計の勘所!!

麻生勝之/宮崎仁「共著

| D 72           | M工防化/ 古剛に L六台                                  |

|----------------|------------------------------------------------|

| 目次             |                                                |

| [CONTENTS]     | 第1章 写真館                                        |

|                | 写真館(1) 産業分野で SoC が 使われているところ 2~3               |

|                | 写真館(2) SoC 搭載ボードの例 4~5                         |

|                |                                                |

|                | 第2章 SoC 選定時のポイント                               |

|                | 2-1 SoCとはどんなものか                                |

| 3 1            | 2-2 CPUおよびメモリの検討での注意点8~9                       |

|                | 2-3 電源仕様の検討での注意点 9~10                          |

|                | 2-4 I/O およびパッケージの検討での注意点 10                    |

|                | <b>第0章</b> A0000 6期再                           |

| 200 1000       | 第3章 AG903の概要                                   |

|                | 3-1 AG903の特徴······11~13                        |

|                | 3-2 OpenVGによる高品位なフォント描画 13~14                  |

| A              | 3-3 ビデオ・キャプチャと画像処理機能15~16                      |

|                | 3-4 パラレル・バス I/F とデバイス・モード <b>17</b>            |

| 4              | 3-5 機能拡張 I/F (EQS I/F)·······18~20             |

| <b>S</b>       | 第4章 AG903を利用した設計時のポイント                         |

| leo val        | 4-1 ピン・マルチプレクス                                 |

| 19- <b>5</b> 7 | 4-2 非同期シリアル I/F ······· 23                     |

| 3              | 4-3 同期シリアル I/F ······ 24                       |

| of the last    | 4-4 パラレル・バス I/F ······· 25                     |

|                | 4-5 I/O 電圧···································· |

| 400 300        | 4-6 電源28~29                                    |

|                | コラム                                            |

|                |                                                |

|                | 第5章 AG903の適用事例                                 |

| 1000           | 5-1 AG903の適用事例1(プログラマブル表示機) ······ 31          |

|                | 5-2 AG903 の適用事例 2 (外観検査装置) · · · · · 32        |

|                |                                                |

## ~写真館(1) 産業分野で SoC が 使われているところ

CPU、メモリ、汎用 I/O、グラフィックス機能などを 1 個の LSI に統合した SoC は、特定用 途向けの高度なシステムをコンパクトに実現できるというのが大きな特徴だ. それを生かして. FA/工場,公共サービス,作業現場,医療など,長期使用されるさまざまな分野の産業用組込 み機器でも幅広く用いられている。ここでは、そのいくつかを紹介しよう。

#### ■FA/ 工場向けの SoC 活用の例

#### プログラマブル表示機を用いた操作盤

工場内では、システムに合わせて製作 した操作盤や, 個々の機器がもつ表示/ 操作パネルが数多く使われている。この ようなパネルでは、画像表示機能やディ スプレイI/F, タッチパネルI/F, カメラ I/F、機器接続用の汎用I/F を備えた SoC を活用して、小型化と高機能化を実現し ている.

射出成型機

チップ・マウンタ

測定器

#### ■公共交通機関向けの SoC 活用の例

#### 新幹線 / 高速鉄道の運転台

#### バスの料金器

鉄道、バスなどの交通機関では、運転台の計器類や料金器、客席の案内表示などの電子化が進んでおり、 多彩な表示パネルによって情報を見やすく伝えている.

#### ■作業現場向けの SoC 活用の例

#### 建設機械の操作パネル

や装置が使われている。複雑な情報の確認や難しい制御が 必要なものも多い、操作の負担を減らすために、針式の計 器と機械式の操作ボタンから、見やすく操作しやすい GUI の表示 / 操作パネルに進化を続けている.

#### 消防車の操作パネル

#### ■医療向けの SoC 活用の例

#### ベッドサイド・モニタ

が活躍している.

検眼機

医療現場では、患者の状態を的確に把握して適切な処置を行うために、 心拍 / 呼吸 / 血圧などのバイタルサインの監視、内視鏡や眼底カメラな ど身体内部の目視検査, 超音波や X 線, NMR(核磁気共鳴)などを利用し た各種の画像検査など、多数の高度な医療電子機器が使用されるように なっている。ここでも、見やすく操作しやすい装置の実現のために SoC

#### 内視鏡

## **1-2** 写真館(2) SoC 搭載ボードの例

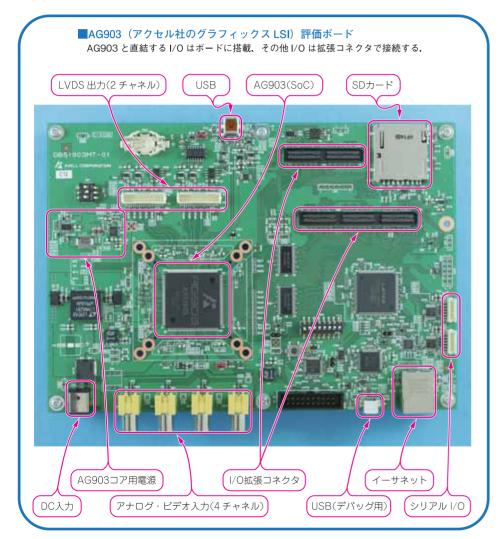

SoC は1チップに CPU、メモリ、周辺機能や高度な専用機能を統合した高機能の LSI なので、多くの I/O は SoC と直結可能だ、そのため、SoC を搭載するボードは、SoC と各 I/O 用コネクタが直結されるシンプルな構成になる。

実際の SoC を搭載したボードの例として、アクセル社が AG903 の開発時に使用したボードを示す。

#### ■IC ソケットを装着した AG903 評価ボード

IC ソケットを装着したボードでは、複数のサンプル品を評価する. 基板のランドと AG903 の端子は、ポゴピンを介して接触する.

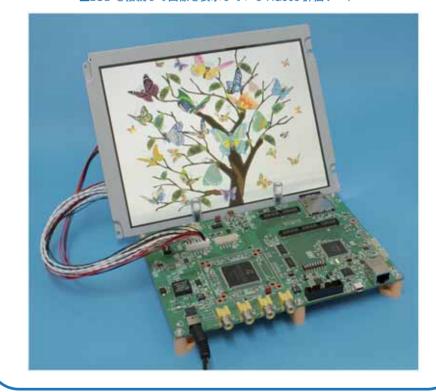

#### ■LCD を接続して画像を表示している AG903 評価ボード

## 第2章 SoC 選定時のポイント

SoC は System-on-Chip の略で、CPU、メモリ、周辺 I/O を含む大規模システムを、1 個のシリコン・チップ上に統合したデバイスです。部品点数の削減、基板面積の縮小などにより、装置の小型化や低コスト化に対する利点が大きく、携帯機器や小型機器を中心に広く使われています。

SoC は ASIC(ユーザが仕様を決めて設計し、半導体メーカで製造するカスタム LSI)の一種であり、もともとはユーザが自社で使うために作っていました。現在では、SoC として作った LSI を製品として外販することも多くなっています。

この第2章では、市販のSoC製品を活用して組み込みシステムを設計するために、SoC選定時に検討すべきポイントについて説明します。

## **2-1 SoC** とはどんなものか

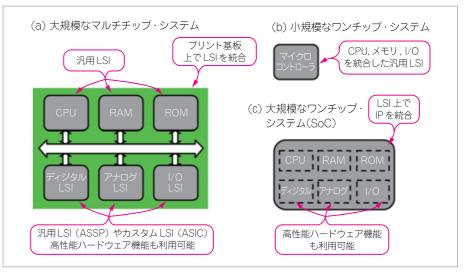

以前は、大規模な組み込みシステムを構築するには、汎用のプロセッサやメモリ、複数の ASSP(特定用途向け標準製品)や、ASIC(特定用途向けカスタム製品)を組み合わせたマルチチップのシステムとして基板に実装することが必要でした(図 2-1(a)). 部品点数が多く、基板 面積が大きくなることから、装置の小型化や低コスト化には限界がありました.

また、小規模な CPU、メモリ、周辺 I/O を統合したマイクロコントローラも古くから使われています (図 2-1 (b)). 小規模なシステムなら 1 チップで構成できる利点をもちますが、CPU の性能、メモリの容量、周辺 I/O の機能などは限定されたものでした.

1990~2000年代にはLSIの集積度が急速に向上し、複数の機能が混在した大規模かつ高性能なシステムを1チップに搭載できるようになりました。それとともにASICの設計・製造技術も進化し、機能ブロックごとにIP(Intellectual Property)として用意された設計データを組み合わせて、大規模なASICを短期間で開発する手法が普及していきました。それによって、ユーザが必要とするシステムを、1個のLSIとして容易に実現できるようになりました。これをSoCと呼んでいます。

容易とは言っても、LSIの開発はNRE(開発の固定コスト)が大きく、同じものを大量生産しないと採算が取れないため、SoC を自社で開発できるユーザは限られています。一方で、ユーザとして開発したSoC を外販したり、半導体メーカが標準製品として開発したSoC を販売することも多くなっています。

それらの市販 SoC によって、少量・多品種生産の装置でも 手軽に SoC の利点が得られるようになりました。ただし、 SoC の選定や設計にはいくつか注意すべき点があります。

#### 図 2-1 組み込みシステムの構成方法

SoC の特徴として、次のような点があげられます。

#### ■ソフトウェアを開発してシステムとして完成させる

SoC は既製品の機能 LSI ではなく、ユーザがソフトウェアを開発して搭載することによって必要な機能を実現し、システムとして完成させるものです。同じ SoC を使って装置を開発しても、ソフトウェアの違いによって差別化することが可能です。

SoCにはCPU、メモリおよびさまざまなハードウェア機能が集積されていますが、ソフトウェアは基本的に搭載されていません。SoCの選定時には、ソフトウェア開発を十分に考慮してCPUを決める必要があります。ただし、一部の機能をファームウェアとして搭載しているSoCもあります。

#### ■1 チップで完結したシステムが得られる

SoC に外付け LSI をいろいろ接続することもできますが、1 チップで完結したシステムにできるのが大きな特徴です。ハードウェアはなるべく内蔵機能を活用し、ソフトウェアで付加機能を実現するというのが SoC の一般的な考え方です。

ただし、DRAMやフラッシュメモリは外付けも多く見られます。これらはCMOSロジックやSRAMとは製造プロセスが異なり、SoC内蔵には若干制約があるためです。また、内蔵メモリは後から追加できないので、外付けで拡張可能にしているSoCもあります。

さらに、製品として市販されているSoCでは、汎用性が高いものを中心にI/O機能を搭載しています。 そのため、あまり一般的でない機能が必要な場合には、必ずしも1チップにこだわらず、外付けでの 拡張も有効な手段となります。その点で、SoCの選定時には拡張性も十分に考慮すべきでしょう。

#### ■一部の機能・性能をグレードアップできない

マルチチップのシステムでは、CPU だけをグレードアップとか、メモリだけをグレードアップするという方法でシステムの機能・性能をグレードアップできます。しかし、SoC は1チップでシステムを構成するため、一部をグレードアップできません。システム設計の途中で CPU 処理性能の不足、バス速度の不足、メモリ容量の不足、消費電力の過多などが判明しても、手戻りはまず不可能です。SoC の選定からやり直すことが必要となり、最悪の場合、それまでの設計作業はぜんぶ無駄になってしまうこともあります。

SoC選定では、マルチチップ・システム以上に慎重な検討・評価が必要です。それも、カタログ・スペックだけで評価するのではなく、目的の SoC が搭載された評価ボードを利用して、実際のハードウェア上で十分な確認を行うことは特に重要です。単に動かすだけではなく、実際に想定している負荷を反映した条件で確認し、負荷の重い処理が複数重なった場合など最悪条件についても考慮が必要です。

#### ■代替品種の入手は期待できない

汎用のプロセッサやマイクロコントローラは、廃品種になった場合でも類似の品種で代替できる可能性があります。しかし、もともと特定用途向けに特化して設計されたSoCでは、簡単に代替できる品種が見つかる可能性は低いでしょう。

組み込み分野では、最終製品のライフサイクルが長いので、それに応じて SoC も長期供給が期待できる製品を選定することが必要です。半導体メーカの側からすれば、SoC は大量に生産して短期間で売り切る方が利益が出やすい製品です。一部の海外メーカでは、最初から長期供給を考えずに製品化していることもあるので注意が必要でしょう。

## 2-2 CPU およびメモリの検討での注意点

CPU 検討時に特に注意すべきポイントは、開発環境や開発リソースの整備状況と、動作周波数と処理性能の関係です。また、動作周波数は内蔵メモリにも関係してきます。

#### ■開発に必要な環境、リソースの整備状況を十分に検討する

SoCではソフトウェアを開発してシステムとして完成させます。そのため、ツール、ライブラリ、ドライバ、ミドルウェア、OSなどを含む開発環境、開発リソースの整備状況について、サードパーティからの供給も含めて十分に検討する必要があります。GUI、イーサネット、USB、ファイル・システム、画像処理、音声処理、セキュリティなどの機能は、OSやミドルウェアを活用する方が簡単に実現できます。

ARM のように複数の半導体メーカが横断的に採用している CPU では、多くのサードパーティから多数のリソースが供給され、充実したエコシステムを形成しています。このような業界標準アーキテクチャは、現在の開発に有利なだけでなく、将来的にもリソースの供給が長く続くことや、代替リソースも豊富であることが期待できます。

#### ■処理性能は、動作周波数だけで決まるわけではない

高い処理性能が要求されるシステムでは、まず動作周波数に目が行きがちです。しかし、SoC の処理性能は単純に動作周波数だけでは決まらなくなっています。

DSP、SIMD、FPUなどの演算アクセラレータ、単純なステップ処理をハードウェアで実行するシーケンサ、高速データ転送を行うDMA機能などを搭載してCPUの負荷を分散すれば、動作周波数が低くても処理性能を大きく向上できます。また、それらを活用して動作周波数を引き下げられれば、システムの消費電力削減にも有利です。

CPU の処理を高速に実行するには、命令フェッチやデータ・リード/ライトなどのメモリ・アクセスの効率化も重要です。単に動作周波数を高くしても、メモリやバスの転送速度にボトルネックを生じると、全体の処理性能が低下してしまいます。

このようなトータルの処理性能は、カタログ・スペックだけで精度良く見積もるのは困難です。評価ボードでの十分な確認が不可欠な項目です。

#### ■内蔵メモリがシステム全体に影響する

SoC にはさまざまなメモリを内蔵していますが、外付けメモリが必要になる場合も少なくありません、DRAM やフラッシュメモリを SoC に内蔵するには制約があるためです。

特に、マイクロコントローラのように内蔵フラッシュメモリ上でプログラムを実行するデバイスでは、フラッシュメモリのアクセス速度が遅いため、システムの動作周波数が上げられなくなります。ARMコアでも、内蔵フラッシュメモリの製品は100MHz以下が多く、外付けフラッシュメモリの製品は200MHz以上の周波数で動作します。

最近の SoC は高集積化が進んだこともあり、高速動作が必要なキャッシュメモリ、ワークメモリ、VRAM などは大容量のものを搭載した品種もあります。必要なメモリを十分に検討して精度よく容量を見積もり、拡張性にも考慮することが必要です。

### 2-3 🤇 電源仕様の検討での注意点

一般に、電源電圧と消費電力の二つの面から検討します。

#### ■電源電圧の種類が多くても問題はない

SoC などの大規模なLSIでは、プロセス・ルールを微細化し、電源電圧を引き下げることによって、集積度と動作速度を向上させてきました。その結果、コア部分の電源電圧は $0.9 \sim 1.2$ V程度に低下しています。一方、周辺回路とのI/O部分などでは、5V、3.3V、2.5V、1.8V など従来からのI/O電圧レベルが使われています。

大規模、高性能の LSI を用いるシステムでは、これらの電源に個別に対応する複数の電源回路が必要です。最近では小型・高効率で使いやすいオンボードの電源モジュールや電源 IC が普及し、POL(Point of Load)電源を簡単に作れます。一般的には電源電圧が SoC 選定の重要問題になることはあまりないでしょう。

### ■消費電力は精密な見積もりが必要

消費電力については、バッテリ動作機器ではきわめて切実な問題です。それ以外の機器でも、 電源容量や発熱について精密な見積もりと十分な検討が必要になります。消費電力が大きい LSI は放熱器が必要であり、管体にもファンが必要になることがあります。

各電源ごとに負荷電流を見積もり、そこからLSIのトータルな消費電力を見積もります. バッテリ寿命を検討する場合は、ボード単位や装置単位での消費電力も見積もります.

SoC に限りませんが、カタログやデータシートに記載されている消費電力は特定条件下での参考値です。回路やソフトウェアによって、消費電力は大きく変わってきます。この場合も、実際のアプリケーションの条件をできるだけ反映させて見積もりを補正し、必要に応じて評価ボードなどで動作させて測定、評価を行う必要があります。

## 2-4 / I/O およびパッケージの検討での注意点

LSI の集積度がきわめて高くなり、内蔵機能はどんどん増えていますが、パッケージのピン数の制約から全機能を同時には使用できません。一方、多ピン化が可能なパッケージには実装上の問題点もあります。それらのバランスを検討することが必要です。

#### ■周辺 I/O はピン・マルチプレクスに注意する

SoC はきわめて多くの I/O 機能を内蔵していますが、パッケージのピン数の制約から、1本のピンを複数の用途に兼用するピン・マルチプレクスを採用しているのが普通です。この場合、ピンに1つの用途を割り当ててしまえば、他の用途には使えなくなります。

SoC の選定時には、ピン・マルチプレクスについて十分に仕様を確認し、必要な機能を同時に使用できるか慎重に検討する必要があります。同じ品種でもパッケージが変わるとピン数とピン・マルチプレクスが変わるので、使いたいパッケージで検討することが必要です。

#### ■実装しやすい QFP、注意が必要な BGA

代表的な表面実装 LSI パッケージには、パッケージ周囲にピンが出ている QFP(Quad Flat Package)と、パッケージ下面にはんだボール端子を並べる BGA(Ball grid array)があります。同じ本体サイズなら、BGA の方がピン数を多くできますし、周囲にピンが出ないので実装面積を小さくできます。しかし、実装面では QFP に利点があります。

QFPの利点は、実装が容易ではんだ不良が少ないこと、実装後にピン状態を目視できること、ピンが変形を許容するため振動や熱応力によるはんだの割れや剥離が起きにくいこと、パッケージ下面に広い放熱面を作れること、配線パターンを描きやすく2層基板や4層基板でも使えることがあります。BGAでは一般的には6層以上の多層基板が必要です。

特別な多ピン化や小型化が要求される用途を除けば、実装が容易で信頼性が高い QFP が広く用いられています。パッケージ選定では、基板占有面積、実装コスト、信頼性などの要求を十分に検討することが必要です。

## 第3章 AG903 の概要

SoCにはさまざまな製品がありますが、第3章~第5章では具体的なSoC製品を例にとって、システム設計のポイントやノウハウを解説していきます。

アクセル社は、さまざまな組み込み機器に高解像度・高精細グラフィックスを搭載するためのグラフィックス LSI を得意とするファブレス半導体メーカです。これまでは、外付けのプロセッサと組み合わせてシステムを構成するための ASSP 製品を主に作ってきました。

最新製品のAG903は、ARM Cortex-A5と大容量 VRAM、各種の周辺機能とI/F、グラフィックス機能とビデオ I/F を統合した SoC 製品です。1 チップでシステムを構成できるので、サイズやコストの制約が大きい組み込み製品で高度なグラフィックスを容易に実現できます。業界標準の Cortex-A シリーズ・コアを採用し、ARM エコシステムや Linux を活用したシステム設計が可能です。

また、AG903 を高機能かつ高性能のグラフィックス LSI として使用し、外付けのホスト・プロセッサと組み合わせてシステムを構成することも可能です。

### **3-1** 〈 AG903 の特徴

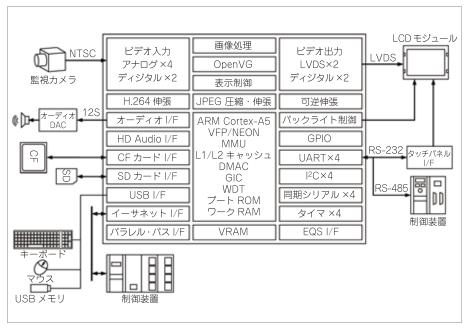

以下に, AG903 の特徴を示します. また, 表3-1 に主な仕様を, 図3-1 にブロック図を示します.

- ▶AG903(型番 AX51903)は、アクセル社の組み込み機器向けグラフィックス LSI

- ▶CPU は ARM Cortex-A5 を内蔵し、Linux の動作も可能

- ▶大容量 VRAM(64MB)をオンチップに搭載

- ▶独立4系統のコンポジット・ビデオ入力が可能

- ▶キャプチャした画像は、画像処理や IPEG 圧縮などが可能

- ▶OpenVG1.1 に対応したベクタ・グラフィックス機能をもち、高品位なフォント描画が可能

- ▶映像2系統出力が可能

- ▶内蔵の H.264 デコーダは、デジタル・サイネージにも利用可能

- ▶USB. CF カード. SD カード. イーサネット. UART. 同期シリアル. I<sup>2</sup>C の各種 I/F を搭載

- ▶ 外付け CPU による AG903 の制御が可能

- ▶QFPパッケージを採用し、ボードの信頼性向上、 コストダウンが図れる

#### 表 3-1 AG903 の主な仕様

| 機能          | 詳細         | 性能                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |

|-------------|------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 内蔵 CPU      | コア, クロック   | ARM Cortex-A5, 400MHz                                                                              |  |  |  |  |  |  |  |  |  |  |  |

|             | FPU        | ARM VFP3/NEON                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

|             | 周辺機能       | MMU, L1/L2 キャッシュ, DMAC, GIC, タイマ                                                                   |  |  |  |  |  |  |  |  |  |  |  |

| 内蔵 VRAM     | 容量         | 512M ビット(64M バイト)                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

| ビデオ入力       | 入力I/F      | 24 ビット・ディジタル ×1 または8 ビット・ディジタル ×2,<br>アナログ ×4                                                      |  |  |  |  |  |  |  |  |  |  |  |

|             | 入力フォーマット   | RGB888/RGB565/YCbCr422(ディジタル)<br>NTSC/PAL コンポジット(アナログ)                                             |  |  |  |  |  |  |  |  |  |  |  |

|             | 入力ドット・クロック | 最大 170MHz                                                                                          |  |  |  |  |  |  |  |  |  |  |  |

| ビデオ出力       | 出力 I/F     | 24 ビット・ディジタル ×1 または 8 ビット・ディジタル ×2,<br>LVDS デュアル ×1 または LVDS シングル ×2                               |  |  |  |  |  |  |  |  |  |  |  |

|             | 出力フォーマット   | RGB888/RGB565/YCbCr422(ディジタル)                                                                      |  |  |  |  |  |  |  |  |  |  |  |

|             | 最大解像度      | 1920×1200, 60Hz(ディジタル)<br>1366×768, 60Hz(LVDS シングル)<br>1920×1200, 60Hz(LVDS デュアル)                  |  |  |  |  |  |  |  |  |  |  |  |

|             | 出力ドット・クロック | 最大 170MHz                                                                                          |  |  |  |  |  |  |  |  |  |  |  |

|             | 総発色数       | 24 ビット                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

|             | ウィンドウ数     | 16 ウィンドウ                                                                                           |  |  |  |  |  |  |  |  |  |  |  |

| 描画          | 対応 API     | OpenVG1.1 準拠 API, AG9 描画 API                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 画像圧縮 / 伸張   | 圧縮方式       | JPEG(圧縮 / 伸張), H.264(伸張), AG9 形式(可逆伸張)                                                             |  |  |  |  |  |  |  |  |  |  |  |

| 画像処理        | 機能         | I/P 変換, クロップ, ノイズ・フィルタ, 色空間変換,<br>HSV/HLS 変換, 縮小, 空間フィルタ, 濃度変換, 閾値<br>処理, ラベリング, ヒストグラム生成, フレーム間演算 |  |  |  |  |  |  |  |  |  |  |  |

| 外部 I/F      | CPU 周辺 I/F | UART×4, 同期シリアル×4, I <sup>2</sup> C×2, タイマ×4,<br>バックライト制御×2, EQS×1, GPI0, デバッガ                      |  |  |  |  |  |  |  |  |  |  |  |

|             | イーサネット     | MII/RMII(10/100M)×1                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|             | USB        | USB2.0(HS/FS/LS)×1(ホスト/ファンクション切替)                                                                  |  |  |  |  |  |  |  |  |  |  |  |

|             | オーディオ      | I <sup>2</sup> S/ 右詰め / 左詰め /TDM×4, HD Audio×1                                                     |  |  |  |  |  |  |  |  |  |  |  |

|             | メディア       | CF $b - k$ (TrueIDE/PC $b - k$ ),<br>SD $b - k$ (SDSC/SDHC/SDIO/MMC)                               |  |  |  |  |  |  |  |  |  |  |  |

| パラレル・バス I/F | バス幅, クロック  | 32/16/8 ビット, 最大 66MHz                                                                              |  |  |  |  |  |  |  |  |  |  |  |

|             | アドレス空間     | 26 ビット(64M バイト)                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

|             | メモリI/F     | SRAM/SDRAM I/F                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| デバイス機能      | バス幅, クロック  | 32/16 ビット, 最大 66MHz                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|             | アドレス空間     | 26 ビット(64M バイト)                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

|             | データ転送モード   | デュアル・アドレス・モード                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 動作電圧        |            | コア:1.15V,I/O:1.8V または3.3V,アナログ:1.8V,<br>VRAM:1.8V                                                  |  |  |  |  |  |  |  |  |  |  |  |

| パッケージ       |            | 256 ピン QFP (底面放熱パッド付き), 28×28mm                                                                    |  |  |  |  |  |  |  |  |  |  |  |

#### 図 3-1 AG903 のブロック図

| ビデオ入力        | 画像処理                | ビデオ出力    |

|--------------|---------------------|----------|

| アナログ×4       | OpenVG              | LVDS×2   |

| ディジタル ×2     | 表示制御                | ディジタル×2  |

| H.264 伸張     | JPEG 圧縮・伸張          | 可逆伸張     |

| オーディオ I/F    | ARM Cortex-A5       | バックライト制御 |

| HD Audio I/F | VFP/NEON<br>MMU     | GPIO     |

| CF カード I/F   | L1/L2 キャッシュ<br>DMAC | UART×4   |

| SD カード I/F   | GIC                 | 2C×4     |

| USB I/F      | WDT<br>プート ROM      | 同期シリアル×4 |

| イーサネット I/F   | ワーク RAM             | タイマ×4    |

| パラレル・バス I/F  | VRAM                | EQS I/F  |

**写真1 AG903 の外観** パッケージは QFP256 ピン, サイズは 28×28mm

## **3-2** < OpenVG による高品位なフォント描画

AG903 の特徴の一つである、OpenVG によるアウトライン・フォント描画について説明します。OpenVG は、クロノス・グループ (The Khronos Group)で作られたオープンでロイヤリティ不要のベクタ・グラフィックス描画用 API です。現行バージョンは 2008 年に発表された OpenVG 1.1 です。

クロノス・グループは、プロセッサ、グラフィックス LSI、PC やサーバ、携帯機器、ソフトウェアなどに関わる 100 社以上の企業が参加している非営利の団体です。さまざまなプラットフォームやデバイス上で動作するオープンな業界標準のグラフィックス API を策定し、普及させることを目的として、2000 年に設立されました。OpenVG の他にも、デスクトップ WS/PC 向け3D/2D グラフィックス API の OpenGL をはじめ、多くの業界標準 API で知られています。

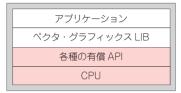

OpenVGは、ハードウェア資源が限られている携帯機器でベクタ・グラフィックスを効率良く実現できるように作られました(図 3-2).

ビットマップ画像をそのままデータ化したラスタ・グラフィックスは、単純に描画できますが、拡大/縮小によって画像品質が劣化する場合があります。ベクタ・グラフィックスは、線の方向と長さ、円の中心と半径などのパラメータで対象の画像を表現したものをデータとしており、拡大/縮小しても高品質の表示ができます。そのかわり、描画するには座標の再計算が必要です。

OpenVG はこの描画作業をハードウェア・アクセラレータで行い、CPU などのシステム・リソースに負担をかけずに、拡大 / 縮小しても品位が低下しないアウトライン・フォントやスケーラブルなベクタ・グラフィクスの描画ができます。

#### 図 3-2 ベクタ・グラフィックスの描画方式

#### (a) OpenVG を用いない描画

#### (b) OpenVG で描画

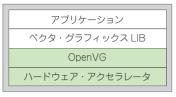

AG903 は、OpenVG 1.1 準拠のアクセラレータを内蔵しており、高品位のフォント描画ができます。アウトライン・フォントは文字の輪郭をベジェ曲線などの曲線を組み合わせたデータで持っており、拡大/縮小しても画像品質が劣化しないのが特徴です。

図3-3 に、文字サイズを拡大した場合の、アウトライン・フォントと非アウトライン・フォントの見え方の違いの例を示します。

#### 図 3-3 文字の拡大方法と見え方の違いの例

非アウトライン・フォントの場合,拡大による品質劣化を防ぐために,文字サイズごとに別のフォント・データをもたせる場合も多く,データ・サイズが問題になります。アウトライン・フォ

ントには、一つのフォント・データでさまざまな 文字サイズを高品位に表示できる利点があります.

PC向けのアウトライン・フォントはフォント・データのサイズが大きいという問題がありましたが、データのサイズが小さい組み込み機器向けのアウトライン・フォントもいろいろ作られています。

最近では、携帯電話、デジタル TV, カーナビ などの機器で手軽にアウトライン・フォントが利用されるようになっています.

## 3-3 〈 ビデオ・キャプチャと画像処理機能

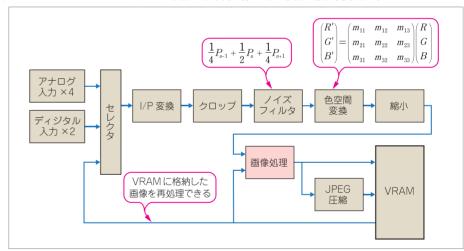

AG903 のビデオ・キャプチャ機能と画像処理機能について説明します.

AG903 は、デジタル 2 系統(8 ビット  $YCbCr \times 2$  または 24 ビット  $RGB \times 1)$  およびアナログ 4 系統(NTSC/PAL コンポジット)のビデオ入力 I/F をもちます。

これらの入力信号に変換や画像処理を行って VRAM に格納することができる,柔軟で強力なビデオ・キャプチャを実現しています。また, VRAM に格納した画像を入力として,再度処理を行ってからキャプチャすることもできます(図 3-4).

セレクタで選択した入力信号がインターレース画像の場合は、I/P 変換機能を用いてプログレッシブ画像に変換できます。また、クロップ(トリミング)、ノイズ・フィルタ、色空間変換に縮小などの機能をもっています。色空間変換機能では、マトリクスに任意の係数を指定することが可能です。

さらに、各種の画像処理や IPEG 圧縮を加えて VRAM に格納することができます.

#### 図 3-4 AG903 のビデオ・キャプチャ機能の概要(同様の処理系統を複数内蔵する)

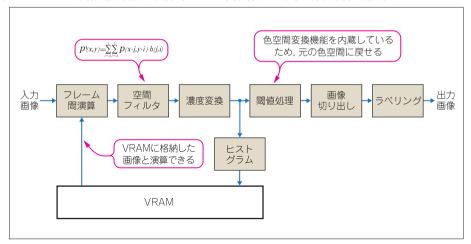

次に、これも AG903 の特徴の一つである柔軟な画像処理機能について説明します.

図3-5 に画像処理の概要を示します。これはフレーム間演算を入力時に行う場合の処理の流れの例ですが、フレーム間演算を画像処理の最後に行うように構成することもできます。

入力画像(今回処理されるフレーム)と VRAM に格納された画像(先行のフレーム)との間でフレーム間演算を行い,動き検出などの処理を行うことができます.これに空間フィルタ,濃度変換などの処理を加えて,さらにヒストグラム生成や閾値処理ができます. 閾値処理で二値化した画像を用いて,画像の切り出しやラベリング(同じ属性の領域を連結)を行って,出力画像を得ることができます.

#### 図 3-5 AG903 の画像処理機能の概要(フレーム間演算を入力時に行う場合の流れ)

フレーム間演算では、あらかじめ VRAM に用意した画像との差分を取ったり、入力画像にオフセットを付けたりすることも可能です。空間フィルタでは、任意の係数を指定することができます。また、濃度変換機能はルック・アップ・テーブル型なので、任意の特性を設定することが可能です

関値処理では任意の関値での二値化が可能で、二値化した画像の面積の計測や画像の切り出しができます。色空間変換機能を内蔵しており、元の色空間に戻すこともできます。さらに、ラベリング機能によって、対象物の位置を特定することもできます。

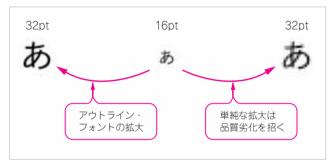

図3-6 に、閾値処理を用いた画像の切り出しの例を示します。AG903 では、入力画像に対してこのような処理をリアルタイムで実行することができます。

#### 図 3-6 閾値処理を用いた画像の切り出しの例 (入力から画像の切り出しまでリアルタイムで処理される)

(a) 入力画像

(b) 入力画像の色相で 二値化した画像

(c) 二値化した画像をもとに 入力画像を切り出した画像 (緑が残る)

## 3-4 パラレル・バス I/F とデバイス・モード

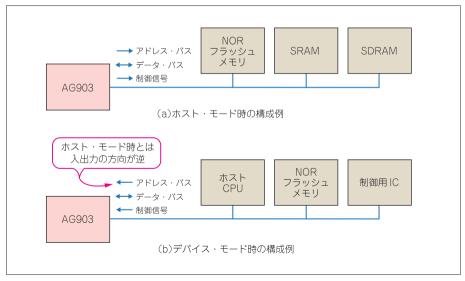

AG903は外部のCPU、メモリ、各種LSIと接続するためのパラレル・バス I/F をもっています。 バス幅は 32 ビット、バス・クロックは最大  $66 \mathrm{MHz}$  です。 アドレスは 26 ビットで、 $64 \mathrm{M}$  バイトのアドレス空間をもちます。

このパラレル・バス I/F は、ホスト・モードとデバイス・モードの二つのモードをもっており、選択して使うことができます( $\mathbf{2}$ -7).

ホスト・モードでは AG903 がアドレスや制御信号を出力してバスを制御します. それに対して, デバイス・モードでは外部のホスト CPU がアドレスや制御信号を出力してバスを制御し, AG903 ではアドレスや制御信号が入力となります.

#### 図 3-7 パラレル・バス I/F のホスト・モードとデバイス・モードの違い

ホスト・モードは、AG903の内蔵 CPU(Cortex-A5)をホストとして、それに NOR フラッシュ・メモリ、SRAM、SDRAM などの大容量メモリや、各種の周辺 LSI を接続するモードです。 1 チップの AG903を中心としてシステムを構成する、 AG903 本来の使い方です。

デバイス・モードは、外部 CPU をホストとして、それに AG903 を接続するためのモードです。この場合は、AG903 をグラフィックス LSI として使用することになります。既存のシステムに対して、表示機能の追加や多画面化などが可能になります。

16 17

## 3-5 〈 機能拡張 I/F (EQS I/F)

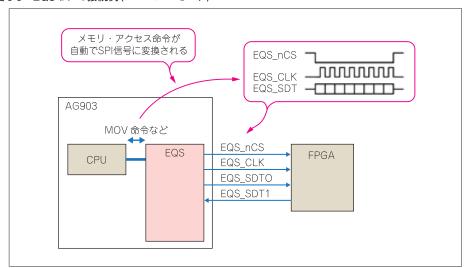

AG903 は、アクセル社独自の機能拡張 I/F として、EQS I/F をもっています.

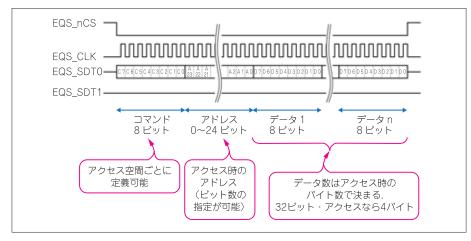

この EQS I/F は、同期シリアル通信として一般的な SPI モード 0(CPOL=0, CPHA=0)と互換の I/F です。1 チャネルの 2 本のデータ線は、送信用と受信用に分かれています。ユーザが独自のコマンドを設定して通信することができます (図 3-8)。

さらに、4本のデータ線をまとめて、同時に4ビットを送信または受信するクワッド・モードがあります。これを用いて伝送を高速化することができます。このとき、データ線は送信と受信の双方向に用いられます。

EQS I/F は、主に FPGA と接続して、AG903 の機能をハードウェアで補完することを想定した I/F です。一般的な SPI と異なる点は、AG903 の場合、内蔵 CPU が所定のメモリ空間にアクセスすると、EQS I/F が自動的に SPI の信号に変換してくれることです。したがって、CPU から見れば特別な I/F を意識せずに、通常のメモリ・アクセスと同様にアクセスすることができます。

#### 図 3-8 EQS I/F の接続例(ノーマル・モード)

ノーマル・モードの書き込み動作時の波形の例を図3-9に示します.

ここでは、EQS I/F は、FPGA に対してまず1バイトの命令を出力し、次に最大24ビットのアドレスを出力し、その後にデータを出力します。データのバイト数はアクセス時のバイト数で自動的に決まり、32 ビット・アクセスなら4バイトになります。

ノーマル・モードの書き込みでは、コマンド、アドレス、データはすべて出力なので、出力データ線(図の例では EQS\_SDT0)のみが使用され、またウェイトなしで連続して出力されます。

#### 図 3-9 書き込み動作時の EQS I/F の波形(ノーマル・モード)

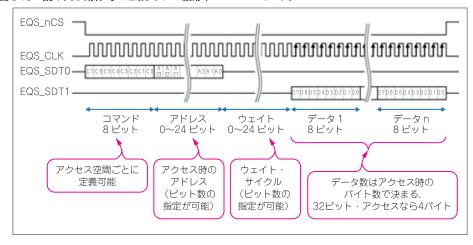

ノーマル・モードの読み出し動作時の波形の例を図3-10に示します.

ここでは、EQS I/F は、FPGA に対してまず1バイトの命令を出力し、次に0~24ビット可変長のアドレスを出力し、所定のウェイト・サイクルの後にデータを読み出します。データのバイト数はアクセス時のバイト数で自動的に決まり、32ビット・アクセスなら4バイトになります。

ノーマル・モードの読み出しでは、コマンド、アドレスは出力なので出力データ線(図の例では EQS\_SDT0)が使用されます。一方、データは入力なので入力データ線(図の例では EQS\_SDT1)が使用され、アドレス出力とデータ入力の間に所定のクロック数のウェイトを挿入できます。ウェイトのクロック数は  $0 \sim 24$  ビット可変長です。

#### 図 3-10 読み出し動作時の EQS I/F の波形(ノーマル・モード)

## 第4章

## AG903 を利用した設計時のポイン

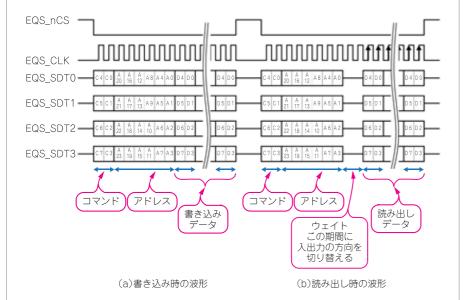

クワッド・モードの波形の例を図 3-11 に示します. 図 3-11(a) が書き込み時, 図 3-11(b) が 読み出し時の波形です.

書き込み時には、FPGA に対してまず1バイトの命令を出力し、次に $0 \sim 24$  ビットのアドレスを出力し、その後にデータを出力します。4本のデータ線(EQS\_SDT $0 \sim EQS_SDT3$ )はすべて出力で、ウェイトなしで連続して出力されます。

読み出し時には、FPGA に対してまず1バイトの命令を出力し、次に $0 \sim 24$ ビットのアドレスを出力し、その後に FPGA からデータを読み出します。コマンド、アドレスの出力時には、4本のデータ線(EQS\_SDT $0 \sim EQS_SDT<math>3$ )はすべて出力になります。所定のウェイト・サイクルの後に、4本のデータ線(EQS\_SDT $0 \sim EQS_SDT<math>3$ )をすべて入力に切り替えて、データを入力します。

ノーマル・モードではコマンド、アドレス、データとも1クロックに1ビットずつ転送しますが、クワッド・モードでは1クロックに4ビットずつ転送できるので、ほぼ4倍に転送を高速化することが可能です。

#### 図 3-11 クワッド・モード時の FOS I/F の波形

この第4章では、アクセル社の AG903 を例として、SoC を用いて実際にシステム設計を行う際の注意点を解説していきます。

I/O ピン割り当ての問題,シリアル I/F やパラレル・バス I/F などのインターフェース設計の問題, I/O 電圧の問題,電源の問題など,一般的に問題になりやすい部分を重点的に取り上げていきます。

### 4-1 🗸 ピン・マルチプレクス

ここでは、LSIパッケージのピン数の制約と、LSI内部の多機能化を両立するためのピン・マルチプレクスについて説明します。

半導体デバイスの集積度の向上によって、SoC やマイコンの高性能化と多機能化が急速に進んでいます。実際の LSI 製品ではピン数をあまり増やすことはできないので、内部がいかに多機能であっても、使用可能な機能は制限されてしまいます。特に、小型・携帯機器ではパッケージ・サイズやパターン面積の制約が厳しくなっています。

また、パッケージ・タイプで見ると、ピン(ボール)数を多くできる BGA は、反面、多層基板が必要となったり、はんだ付け後に接続状態を確認できないなど信頼性や実装コストに問題があります。全ピンを目視可能で実装が容易な QFP は、ピン数の制約がより大きいという問題があります

AG903 は、パッケージ・サイズの小型化と実装のしやすさを重視して、256 ピン QFP となっています。

ピン数の制約と内部の多機能化を両立するため、AG903 のほとんどの I/O ピンは、1 本のピンに複数の機能を割り当てるピン・マルチプレクスを採用しています。そのため、内部機能があっても、同じ I/O ピンを他の機能で使うために利用できないという問題が生じます。システム設計のなるべく早い段階で、使用したい I/F とそれに必要なピンをしっかり洗い出して、それらの I/F を同時に使用できるか入念な確認が必要となります。

使用したい I/F が同時使用できない場合,別の I/F で代替するなどのやりくりで解決できることもありますが,その I/F の使用をあきらめるとか,外付けの I/F を追加しなければならないこともあります.最悪の場合,SoC の選定からやり直しが必要になることもあるので,注意が必要です.

また、設計の初期段階でぴったりと収まった状態だと、その後の設計の過程で仕様変更があったときに、どうにも対処できなくなることがあります。ピン割り当ては余裕を見ておくことが必要です。

20

#### 表 4-1 同時に使用可能な機能の概要

|                 | パックライト制御0 | パックライト制御1 | タイマ1/0  | 16bit パラレル・バス | 32bitパラレル・バス | CF カード (TrueIDE) | CFカード (PCカード) | SDRAM | NOR フラッシュ・メモリ | SD 九一ド | SPIフラッシュ・メモリ | 同期シリアル0 | 同期シリアル1 | 同期シリアル2     | 同期シリアル3 | UARTO       | UART1   | UART2 | UART3 | イーサネット (MII) | イーサネット (RMII) | HD Audio | EQS     |

|-----------------|-----------|-----------|---------|---------------|--------------|------------------|---------------|-------|---------------|--------|--------------|---------|---------|-------------|---------|-------------|---------|-------|-------|--------------|---------------|----------|---------|

| バックライト制御 0      |           | 0         | ×       | Δ             | Δ            | 0                | 0             | 0     | 0             | 0      | 0            | 0       | 0       | 0           | 0       | 0           | 0       | 0     | 0     | 0            | 0             | 0        | $\circ$ |

| パックライト制御1       | 0         |           | $\circ$ | 0             | 0            | 0                | 0             | 0     | 0             | 0      | 0            | 0       | ×       | 0           | 0       | 0           | ×       | 0     | 0     | 0            | 0             | 0        | $\circ$ |

| タイマ1/0          | ×         | 0         |         | Δ             | Δ            | 0                | 0             | 0     | 0             | 0      | 0            | 0       | $\circ$ | 0           | 0       | 0           | 0       | 0     | 0     | 0            | 0             | 0        | $\circ$ |

| 16bit パラレル・バス   | Δ         | 0         | Δ       |               | 0            | 0                | 0             | 0     | 0             | Δ      | 0            | 0       | 0       | 0           | 0       | 0           | 0       | Δ     | 0     | Δ            | 0             | 0        | $\circ$ |

| 32bit パラレル・バス   | Δ         | 0         | Δ       | 0             |              | ×                | ×             | 0     | 0             | Δ      | 0            | 0       | 0       | X           | 0       | 0           | 0       | Δ     | 0     | Δ            | ×             | ×        | $\circ$ |

| CFカード (TrueIDE) | 0         | 0         | 0       | 0             | ×            |                  | 0             | 0     | $\circ$       | 0      | 0            | 0       | $\circ$ | 0           | 0       | 0           | $\circ$ | Δ     | 0     | 0            | 0             | 0        | $\circ$ |

| CFカード (PCカード)   | 0         | 0         | $\circ$ | $\circ$       | ×            | $\circ$          |               | 0     | $\circ$       | 0      | 0            | 0       | $\circ$ | 0           | 0       | 0           | $\circ$ | Δ     | 0     | 0            | 0             | 0        | $\circ$ |

| SDRAM           | 0         | 0         | 0       | 0             | 0            | 0                | 0             |       | 0             | 0      | 0            | 0       | 0       | 0           | ×       | 0           | $\circ$ | 0     | ×     | Δ            | 0             | 0        | $\circ$ |

| NOR フラッシュ・メモリ   | 0         | $\circ$   | $\circ$ | 0             | 0            | 0                | 0             | 0     |               | 0      | 0            | 0       | $\circ$ | 0           | $\circ$ | 0           | 0       | 0     | 0     | $\triangle$  | 0             | $\circ$  | $\circ$ |

| SDカード           | 0         | 0         | 0       | Δ             | Δ            | 0                | 0             | 0     | 0             |        | 0            | 0       | 0       | 0           | 0       | 0           | 0       | 0     | 0     | ×            | 0             | 0        | $\circ$ |

| SPIフラッシュ・メモリ    | 0         | 0         | 0       | 0             | 0            | 0                | 0             | 0     | 0             | 0      |              | ×       | 0       | 0           | 0       | 0           | 0       | 0     | 0     | 0            | 0             | 0        | Δ       |

| 同期シリアル 0        | 0         | 0         | 0       | 0             | 0            | 0                | 0             | 0     | 0             | 0      | ×            |         | 0       | 0           | 0       | 0           | 0       | 0     | 0     | 0            | 0             | 0        | ×       |

| 同期シリアル 1        | 0         | ×         | 0       | 0             | 0            | 0                | 0             | 0     | 0             | 0      | 0            | 0       |         | 0           | 0       | 0           | ×       | 0     | 0     | 0            | 0             | 0        | $\circ$ |

| 同期シリアル 2        | 0         | 0         | 0       | 0             | ×            | 0                | 0             | 0     | 0             | 0      | 0            | 0       | 0       | $\setminus$ | 0       | 0           | 0       | 0     | 0     | ×            | ×             | 0        | $\circ$ |

| 同期シリアル3         | 0         | 0         | 0       | 0             | 0            | 0                | 0             | ×     | 0             | 0      | 0            | 0       | 0       | 0           |         | 0           | 0       | 0     | ×     | 0            | 0             | 0        | $\circ$ |

| UARTO           | 0         | 0         | 0       | 0             | 0            | 0                | 0             | 0     | 0             | 0      | 0            | 0       | 0       | 0           | 0       | $\setminus$ | 0       | 0     | 0     | 0            | 0             | 0        | $\circ$ |

| UART1           | 0         | ×         | 0       | 0             | 0            | 0                | 0             | 0     | 0             | 0      | 0            | 0       | ×       | 0           | 0       | 0           |         | 0     | 0     | 0            | 0             | 0        | $\circ$ |

| UART2           | 0         | 0         | 0       | Δ             | Δ            | Δ                | Δ             | 0     | 0             | 0      | 0            | 0       | 0       | 0           | 0       | 0           | 0       |       | 0     | 0            | 0             | 0        | $\circ$ |

| UART3           | 0         | 0         | 0       | 0             | 0            | 0                | 0             | ×     | 0             | 0      | 0            | 0       | 0       | 0           | ×       | 0           | 0       | 0     |       | 0            | 0             | 0        | 0       |

| イーサネット(MII)     | 0         | 0         | 0       | Δ             | Δ            | 0                | 0             | Δ     | Δ             | ×      | 0            | 0       | 0       | ×           | 0       | 0           | 0       | 0     | 0     |              | 0             | ×        | $\circ$ |

| イーサネット(RMII)    | 0         | 0         | 0       | 0             | ×            | 0                | 0             | 0     | 0             | 0      | 0            | 0       | 0       | X           | 0       | 0           | 0       | 0     | 0     | 0            |               | ×        | 0       |

| HD Audio        | 0         | 0         | 0       | 0             | ×            | 0                | 0             | 0     | 0             | 0      | 0            | 0       | 0       | 0           | 0       | 0           | 0       | 0     | 0     | X            | X             |          |         |

| EQS             | 0         | 0         | 0       | 0             | 0            | 0                | 0             | 0     | 0             | 0      | Δ            | X       | 0       | 0           | 0       | 0           | 0       | 0     | 0     | 0            | 0             | 0        |         |

○: 同時使用可能 △: 同時使用に制限あり ×: 同時使用不可

表 4-1 に、ピン・マルチプレクスされた I/O を対象として、AG903 の同時に使用可能な機能の概要をまとめて紹介します。AG903 は 256 本のピンをもっているので、同時に使用できない機能がそれほど多いわけではありません。ただし、全く同時に使用できない機能(表の  $\times$  印) 以外にも、同時に使用するには制限が付けられている機能(表の $\triangle$ 印)もあるので、注意が必要です

また、この表はAG903の各I/F機能が同時使用可能かどうかを簡単に示しただけのものです。 実際に設計を行う場合は、データシートやユーザーズ・マニュアルなどを 詳細に調べて、ピン機能の重複や機能制限に引っかからないことを確認す ることが必要です。

## **1-2** < 非同期シリアル I/F

AG903 の非同期シリアル I/F について説明します.

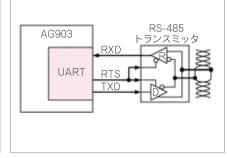

AG903 は 4 チャネルの非同期シリアル I/F (UART0  $\sim$  3)を内蔵しています。各チャネルの I/O 信号は TXD、RXD、CTS、RTS の 4 線ですが、一般的な周辺機器 I/F としてはこれで十分と考えられます。ただし、モデムなど EIA/TIA 規格 (ITU-T 規格)の全信号が必要な I/F の場合は、RI、DTR、DSR、DCD の各制御信号を GPIO (汎用 I/O ポート) に割り当て、ソフトウェアで制御する必要があります。 **図 4-1** に接続例を示します。

AG903 の UART I/F は、送信時、受信時の割り込み機能をもち、受信タイムアウト割り込みも可能です。GPIO 入力信号はすべて割り込み信号として使えるので、GPIO に割り当てた信号でも割り込みによる制御ができます。

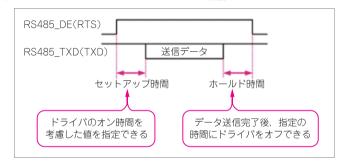

また、AG903のUART I/F は RS-485 ドライバの送信制御ができます。RS485 は複数のドライバ/レシーバを接続して任意間の伝送ができる時分割バスなので、ドライバ出力の 3 ステート制御を行う必要があります。AG903では、RS-485 ドライバの送信制御信号は RTS に割り当てられています(図 4-2) 図 4-3 に RS485 の送信タイミングの例を示します。

図 4-1 AG903 の UART I/F と モデムの接続例

AG903

UART (DTE) RXD CTS RTS RTS DTR RI DSR DCD 単純 DCD 通信

図 4-2 AG903 の UART I/F と半二重 RS-485 トランスミッタとの接続例

図 4-3 AG903 の UART I/F による RS-485 送信タイミング

## **4-3 〈** 同期シリアル I/F

AG903の同期シリアル I/F について説明します.

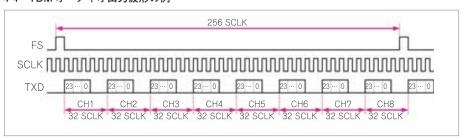

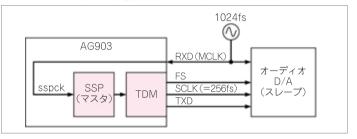

AG903 は 4 チャネルの SPI 対応同期シリアル I/F (SSP0  $\sim$  3)を内蔵しています。SSP I/F は  $I^2S$  (Inter-IC Sound) および TDM オーディオにも対応し、オーディオ用 ADC、オーディオ用 DAC、DSP、ディジタル・フィルタなどのオーディオ・デバイスと容易に接続できます。TDM オーディオで使用する場合は、1 チャネルの SSP I/F でマルチ・チャネルの入力または出力のいずれか、2 チャネルの SSP I/F で入出力を同時に使用できます。

外部からマスタ・クロックを供給する場合は、SSP I/F の RXD 端子を用います。SSP I/F では動作モードに応じてクロック周波数に制限があるため、AG903 と接続するデバイス側の仕様にも注意が必要です。たとえば、マスタ・モードで TDM オーディオ出力する場合、AG903 の SSP クロック周波数  $f_{SDCIK}$  は、出力クロック周波数  $f_{SCLIK}$  の 4 倍以上が必要です。

マスタ・モード、TDM オーディオ出力、256 倍オーバ・サンプリング、外部マスタ・クロックの場合の出力波形の例を**図 4-4** に、オーディオ用 D/A コンバータとの接続例を**図 4-5** に示します。

このとき、出力クロック周波数は $f_{SCLK}=256 \times f_S$ なので、AG903と D/A コンバータに供給する外部マスタ・クロックは少なくとも $f_{MCLK}=4 \times 256 \times f_S=1024 \times f_S$  に選ぶ必要があります。 $f_{SCLK}=12.288$ MHz、 $f_{MCLK}=49.152$ MHz となります。 $f_{MCLK}$  が高くなるため、D/A コンバータの対応周波数範囲を確認する必要があります。

#### 図 4-4 TDM オーディオ出力波形の例

#### 図 4-5 TDM オーディオ出力使用時のオーディオ D/A 接続例

## **4-4** / パラレル・バス I/F

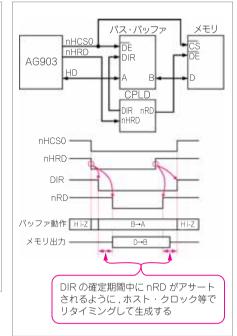

AG903 の外部バスであるパラレル・バス I/F について、設計上の注意点を説明します.

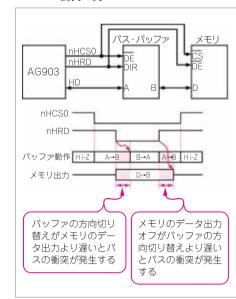

一般に、マイコンなどの外部バスに複数のメモリやLSIを接続していくと、負荷電流が過大になってDC電圧レベルを満たせなくなったり、負荷容量が過大になってAC特性を満たせなくなる恐れがあります。その場合には、駆動能力が高いバス・バッファを挿入することが必要になります。

ただし、バス・バッファには多少の遅延時間があるため、使用するバス・バッファやデバイスの特性によっては、バスの衝突が発生する可能性があります。**図 4-6** に、メモリ・リード時に発生するバス衝突の例を示します。

このような場合,バスの衝突を避けるために、CPLD などを用いてバス制御信号を生成し直すなどの対策が必要になります(図 4-7).

なお、SDRAM と CF カード I/F は、バス・バッファを使用せず、AG903 と直結する必要があります

#### 図 4-6 メモリからのリード時に発生する バス衝突の例

図 4-7 CPLD を用いてリード信号を 生成する例

## 4-5 < 1/0 電用

AG903のI/O電圧とレベル変換の方法について説明します.

AG903 では、I/O 電圧は 3.3V と 1.8V を選択できます。一般に、消費電力や放射電磁雑音に関しては 1.8V I/O の方が有利です。

1.8 V~I/O~b~2.3 V~I/O~b~E接続したり、それ以外のI/O~aEE b~AG903~bC 接続する場合には、レベル変換が必要です。単方向I/O~bC のレベル変換は降圧または昇圧だけを行うので、比較的簡単です。

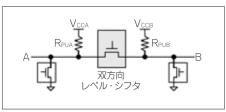

I<sup>2</sup>Cバス、パラレル・バス、SPI(クワッド・モード)、CFカード、SDカードなどの双方向 I/O の場合は、双方向タイプのレベル・シフタを使用して接続する必要があります。レベル・シフタの選択や使い方にも十分な注意が必要です。なお、双方向 I/O でよく使われるバス・スイッチは、各種の I/O 電圧に対応するものがありますが、それ自体は基本的にレベル変換機能はありません。

代表的な双方向レベル・シフタには、オープン・ドレイン型とプッシュプル型があり、それ ぞれ特徴があります。

#### ■オープン・ドレイン型の特徴と注意すべき点

オープン・ドレイン型の双方向レベル・シフタは、二つのオープン・ドレイン出力の間を FETで接続した構造になっています(図 4-8). 構造が簡単という利点がありますが、高速信号 には向きません.

図 4-8 オープン・ドレイン型の双方向 レベル・シフタを用いた回路構成例

図 4-9 プッシュプル型の双方向レベル・シフタ を用いた回路構成例

オープン・ドレイン型は、 $I^2C$  のように接続されるドライバがもともとオープン・ドレインであるような I/F には適しています。

ただし、一般的には信号電圧の立ち上がり時間が長いため、比較的低速の用途に限られてしまう問題があります。オープン・ドレイン出力は、立ち下り時はドライバがオフ⇒オンに遷移して、アクティブに電流を引き込むため高速に動作します。しかし、立ち上がり時はドライバがオン⇒オフに遷移して、プルアップ抵抗を通じて寄生容量に電荷が蓄えられるため低速になってしまいます。

オープン・ドレイン出力の立ち上がり時間を少しでも短くするには、プルアップ抵抗の抵抗

値を小さく選ぶ必要があります。このときの抵抗値は、デバイスの入出力電流の動作条件から 外れないように注意して設計することが必要です。また、動作条件の範囲だとしても、プルアッ プ抵抗を小さくすることによって消費電流が増加することにも注意が必要です。

たとえば、立ち上がり時間 tr=5ns を得るのに必要な抵抗値と、そのときのドライバの電流値を実際に計算してみましょう。両ポートの合計負荷容量を C=40pF、プルアップ抵抗値を  $R_{PUA}=R_{PUB}=R$ . High 電圧を  $V_{H}$ . 電源電圧を  $V_{CCA}=V_{CCB}=V_{CC}=3.3V$  とすれば、

立ち上がり時間

$$t_r$$

=  $-C \cdot \frac{R}{2} \cdot \ln(\frac{V_{CC} - V_H}{V_{CC}})$  より、

$$\mathcal{I} ルアップ抵抗 R = -\frac{2t_r}{C \cdot \ln(\frac{V_{CC} - V_H}{V_{CC}})} = -\frac{2 \times 5 ns}{40 \, pF \cdot \ln(\frac{3.3V - 2V}{3.3V})} \stackrel{.}{=} 268 \, \Omega$$

となります したがって Low 時の引き込み電流 Lは

$I_1 = 3.3 \text{V} / 268 \Omega = 12.3 \text{m A}$

とかなり大きな値になってしまうことが分かります。

なお、ここでは簡単のために  $V_{CCA}$  と  $V_{CCB}$  を同じ電圧、 $R_{PUA}$  と  $R_{PUB}$  を同じ抵抗値として計算しましたが、実際のレベル・シフタでは  $R_{PUA}$   $\neq$   $R_{PUB}$ ,  $V_{CCA}$   $\neq$   $V_{CCB}$  なので、計算式は若干変わります。

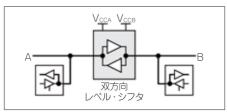

#### ■プッシュプル型の特徴と注意すべき点

プッシュプル型の双方向レベル・シフタは、二つのプッシュプル出力の間を双方向バッファで接続した構造になっています(図 4-9). 衝突を防ぐために自動方向検出機能を内蔵し、高速動作が可能です

プッシュプル型で注意すべき点は、レベル・シフタの出力に外部プルアップ/プルダウン抵抗を接続することが推奨されていないことです。CFカードやSDカードのように規格上プルアップ抵抗の使用が決められているI/Fの場合や、信号の初期値を決めるためにプルアップ/プルダウン抵抗を使いたい回路の場合に問題になります。

プッシュプル型の双方向レベル・シフタは、自動方向検出を実現するために、バス・ホール ド回路と同様に.

- (1)規定を超える電流を流すことによってレベルが反転する(オーバードライブ).

- (2)レベルを保持するためにドライブ可能な電流値に制限がある.

という特徴をもっています。そのため、外部にプルアップ / プルダウン抵抗があると、レベルを保持できる電流値の制限を超えてしまう可能性があります。

たとえば、Low レベルを保持できる電流の規定(ホールド電流の最小値など)が  $75\,\mu\,\mathrm{A}$  の場合の外部プルアップ抵抗 R の最小値は

$R = (V_{CC} - V_L)/I = (3.3V - 0.8V)/75 \mu A = 33k \Omega$

と計算できます。この場合、 $33k\Omega$ より小さいプルアップ抵抗を使用すると Low レベルの保持が保証されず、レベル不定に陥る可能性があります。

特に問題となるのは、たとえば信号の初期値を High にするためにプルアップ抵抗を入れた

場合、それに反してレベル・シフタが出力を Low レベルにしようとすると、High と Low の間 で出力が振動的になることもあります。この異常動作は、プルアップ抵抗をレベル・シフタが ドライブしている時だけ発生するので注意が必要です

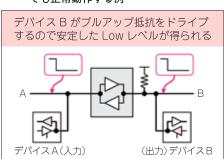

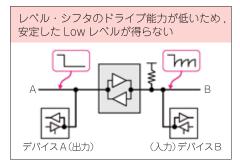

図 4-10 ~ 4-11 は、デバイス A. Bの間を双方向レベル・シフタで接続し、B側にプルアッ プ抵抗を入れた例です。信号の方向が B⇒A のとき、デバイス B がプルアップ抵抗をドライブ するので、出力は安定です、しかし、信号の方向が A⇒B のときは、レベル・シフタがプルアッ プ抵抗をドライブするのでドライブ能力不足となり、出力が不安定になります。

図 4-10 プッシュプル型の双方向レベル・ シフタにプルアップ抵抗を接続し ても正常動作する例

図 4-11 プッシュプル型の双方向レベル・シフタ にプルアップ抵抗を接続して異常動作す る例

AG903の電源供給や、基板の電源パターンの設計について説明します。

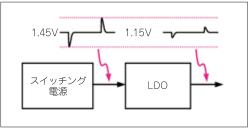

AG903 に必要な電源は、コア用の 1.15V、内蔵 VRAM 用およびアナログ用の 1.8V、I/O 用 の3.3V または1.8V の3種類です。このうちコア用電源は高負荷時にも高い電圧精度が要求さ れるため、電源設計に十分な注意が必要です。

コア用電源の動作条件は1.15V±5%です。ただし、1.15Vの5%はわずか57.5mVですから、 電圧精度が高い電源(IC やモジュール)を使用するとともに、さまざまな要因による電圧変動を 十分に抑える必要があります.

1.15V 電源としては、外付け抵抗で出力電圧を決めるタイプの可変出力電源を使うことが多 いでしょう. この場合の電圧精度は、電源自体の精度だけでなく使用する抵抗の許容差や温度 係数に依存するので、抵抗の選択にも十分な注意が必要です。また、ディジタル値で出力電圧 を設定するタイプの可変出力電源を使用すれば、外付け抵抗は不要になります.

さらに、負荷電流が大きくなると、負荷変動による過渡的な電圧変動や、負荷電流と配線抵 抗による電圧降下も大きくなります。

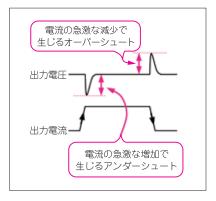

静的には十分な電圧精度をもつ電源でも、負荷電流の急激な変動によって出力電圧に大きな オーバーシュート/アンダーシュート(負荷過渡応答)が生じて、コア電圧の動作条件を超えて しまう可能性があります(図 4-12). それを防ぐには、負荷過渡特性の優れた電源を選ぶことが 必要です、メーカによっては、シミュレーションで事前確認することもできます。

また。高速応答品のLDOは出力電圧の変動を低減する効果が高く ポスト・レギュレータ として活用することができます(図 4-13).

出力電圧のオーバーシュート/アン ダーシュートの例

図 4-12 出力電流の急激な変化により生じる 図 4-13 高速応答品の LDO によるオーバー シュート/アンダーシュートの低減 イメージ

負荷変動の影響を適切に評価するには、負荷電流の変動を知ることが必要です。SoC の消費 電流をリアルタイムに計測できれば、負荷変動の影響を精度良く見積もれます。

ただし、電流計測用にシャント抵抗などを挿入すると、それ自身の電圧降下によって電圧マー ジンが減少してしまいます.回路に影響を与えずに消費電流をモニタできるICとして. LT3071(リニアテクノロジー)があります。アクセル社が提供している AG903 評価ボードには、 LT3071 を搭載しており、必要な電源性能の見積りに役立ちます。

電源から負荷までの配線の部分でも、負荷電流と配線抵抗による電圧変動が生じます(1). た とえば、出力電圧精度2%(=23mV)、最大消費電流2A、負荷過渡応答性能30mVと仮定した場合、 配線抵抗の値は.

$(57.5 \text{mV} - 23 \text{mV} - 30 \text{mV})/2 \text{A} = 4.5 \text{mV}/2 \text{A} = 2.25 \text{m} \Omega$

以下にする必要があります。さらに、温度係数やビアの抵抗値も考慮する必要があります。た だし. 最大消費電流は複数の電源端子の合計値であるため, 1端子当たりで見れば配線抵抗の 条件はもう少し緩和されます.

プリント基板設計時には、IR ドロップ・シミュレーションなどを行って、電圧降下の状態を 事前に確認することが重要です.

◆参考文献◆(1)月本誠士;電源とグラウンドの配線テクニック. トランジスタ技術 2005年6月号, pp.131~139, CQ 出版(株)

## 第5章 AG903 の適用事例

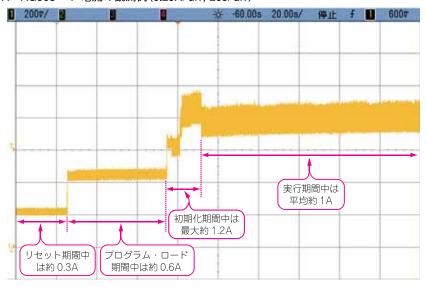

#### AG903 コア電流の観測

図AにLT3071の出力電流モニタ機能を利用した、AG903コア電流の観測例を示します. ノイズの影響を除くため、基板とパッシブ・プローブは変換コネクタを介して同軸コネクタ(MMCX)で接続しています。測定は電圧で行いますが、1.25A/Vで電流に換算できます。図Bに、観測に利用したテスト用プログラムの実行中の様子を示します。

#### 図 A AG903 コア電流の観測例 (0.25A/div. 20s/div)

#### 図 B プログラム実行中の表示画面

画面全体は1600×1200ドットでLVDS出力して表示. 左上と右上はNTSCキャプチャ画像(640×480ドット). 左下はOpenVGによる描画画像(800×600ドット). 右下はH.264伸張画像(800×600ドット). 動画素材(320×240ドット)はUSBメモリから読み出し、H.264伸張したのち800×600ドットに拡大. 灰色背景のみが静止画.

## **5-1 〈** AG903 の適用事例 1 (プログラマブル表示機)

図 5-1 は、タッチパネルで FA 機器の操作・監視を行うための表示盤への適用事例です。多彩な I/F をもつプログラマブル表示機を、AG903 の豊富な I/F 機能で実現しています。

#### 図 5-1 プログラマブル表示機の構成例

メインの表示機能は、LVDS I/Fに LCD モジュールを接続して画像表示を行います。タッチパネルの接続は、一般的な RS-232 I/F を用います。

UART (RS-232 I/F, RS-485 I/F), イーサネット I/F を用いて、PLC などの制御装置、計測装置と接続できます。 AG903 では、RS-232 と RS-485 はハードウェアによるフロー制御やドライバ制御を活用でき、通信の信頼性を高められます。

アナログ・ビデオ入力 I/F にカメラを接続して、監視映像などを表示できます。CF カード I/F や SD カード I/F を利用してログなどをメディアに記録できます。USB I/F にはキーボード、マウスなどの操作デバイスや、USB メモリを接続できます。

H.264 伸張機能を利用して、操作方法を説明する動画などを再生できます。オーディオ I/F から操作音や音声ガイダンスを出力できます。

30 31

### 5-2

### AG903の適用事例2(外観検査装置)

図 5-2 は、製品の外観を検査する画像検査装置への適用事例です。高精度、高速な検査が必要な場合は組み込み用 PC を用いてシステム化するのが一般的ですが、簡単な検査であれば AG903 の前処理機能を活用してコンパクトに実現できます。

LVDS I/Fに LCD モジュールを接続し、入力画像や検査状態をリアルタイム表示します。 検査用のモノクロ・カメラをアナログ・ビデオ入力 I/F に接続できます。

製造ラインをコントロールする制御装置との接続は、UART(RS-232 I/F, RS-485 I/F)、イーサネットI/Fなどを利用します。制御装置からのトリガ信号をタイマI/Fに入力することによって、カメラのシャッター制御などが可能です。

良品 / 不良品の判定には、AG903 の前処理機能を用いて次のようなことが行えます。

- (例1)対象物を二値化し、面積を計測. 画素数が所定の範囲であれば良品とする(図5-3).

- (例2)あらかじめ用意した良品画像と入力画像との差分画像を二値化し、画素数を計測。画素数(良品画像との差)が所定の範囲であれば良品とする。

#### 図 5-2 外観検査装置の構成例

図 5-3 対象物の面積を 計測して判定

著

## 者

愛するエンジニア. ジュギング中に「やり切るまで.

●麻牛 勝之 (あそう・かつゆき)

ジョギング中に「やり切るまで続けないのはいけない」と考える毎週末.

株式会社 アクセル スキーとお酒をこよなく

略

●宮崎 仁 (みゃざき・ひとし)

有限会社 宮崎技術研究所. 一人で何役もこなすユーティリティ・エンジニアを目指すも、なかなか道はけわしいと思う今日この頃.

#### ●本誌掲載記事の利用についてのご案内

本誌掲載記事には著作権があり、また工業所有権が確立されている場合があります.したがって.個人で利用される場合以外は所有者の承諾が必要です.

また,掲載された回路,技術,プログラムを利用して生じたトラブルなどについては,小社ならびに著作権者は責任を負いかねますのでご了承ください.

本誌に記載されている社名,および製品名は,一般に開発メーカの登録商標または商標です。なお本文中では™、®、®の各表示を明記しておりません。

#### ●本書に関する質問について

電子メール,電話でのお問い合わせは応じかねます.文章,数式などの記述上の不明点についてのご質問は,必ず往復はがきか返信用封筒を同封した封書でお願いいたします.ご質問は著者に回送し直接回答していただきますので,多少時間がかかります.また,本書の記載範囲を超えるご質問には応じられませんので,ご了承ください.

## トランジスタ技術 特別小冊子(非売品)

### SoCを用いたシステム設計の勘所!!

著 者 麻生 勝之/宮崎 仁

発行人

寺前 裕司

編集人

中元 正夫

発行所 CQ 出版株式会社

〒112-8619 東京都文京区千石 4-29-14

(03)5395-2123(出版部) (03)5395-2141(販売部) 振替 00100-7-10665

Printed in japan

(無断転載を禁じます)

乱丁,落丁はお取り替えします デザイン/DTP(株)イー・スリー・フ